二维铁电场效应晶体管(FeFET)结合了二维半导体的原子级沟道优势与铁电非易失特性,在高能效计算与存储领域展现出巨大潜力。钙钛矿铁电氧化物(如 BaTiO3,BTO)凭借其超高介电常数及强铁电极化特性,在构建低功耗、高性能二维 FeFET 方面具有本征优势。然而,传统氧化物苛刻的外延生长条件难以兼容二维材料与主流 CMOS 工艺,严重阻碍了这一技术路线的微缩化应用。近年来,自支撑薄膜技术的兴起为范德华(vdW)异质集成提供了理想的解决方案,有望打破晶格匹配限制,实现铁电功能层与任意半导体沟道的自由组合。然而,这一新兴路线在实际器件化进程中仍面临严峻挑战:一方面,尽管薄膜具备优异的超弹性,但其释放的内禀应力在传统转移过程中会诱发难以控制的卷曲形变,成为阻碍高质量集成的工艺壁垒;另一方面,氧化物中普遍存在的氧空位缺陷往往引发严重漏电流,导致器件难以实现可靠的极化翻转,这一长期存在的难题严重限制了其实际应用。

近日,复旦大学微纳电子器件与量子计算机研究院沈健/郭杭闻课题组、石武课题组与中国科技大学合肥微尺度物质科学研究中心王凌飞课题组等密切合作,提出了面向二维铁电场效应晶体管的高介电自支撑氧化物薄膜范德华集成新策略。该策略采用可扩展的抗卷曲集成工艺,利用聚甲基丙烯酸甲酯(PMMA)辅助转移技术成功攻克了自支撑薄膜的形变难题。同时,团队结合器件微缩化工艺,通过缩减功能结面积,在无需引入介质阻挡层的情况下有效抑制了漏电,实现了本征铁电翻转。基于该策略构建的 BTO/MoS2 FeFET 展现出卓越电学性能:拥有0.22 V/nm 超大存储窗口、高介电常数及理想亚阈值摆幅。在此基础上,团队进一步制备了顶栅铁电晶体管器件阵列,成功演示了非易失逻辑与神经形态计算等多功能应用,有力验证了该技术在未来高能效电子领域的可靠性与可扩展性。相关成果以 “Integration of freestanding high-k oxide membranes for two-dimensional ferroelectric field-effect transistors”为题于12月14日发表于《Advanced Science》期刊。

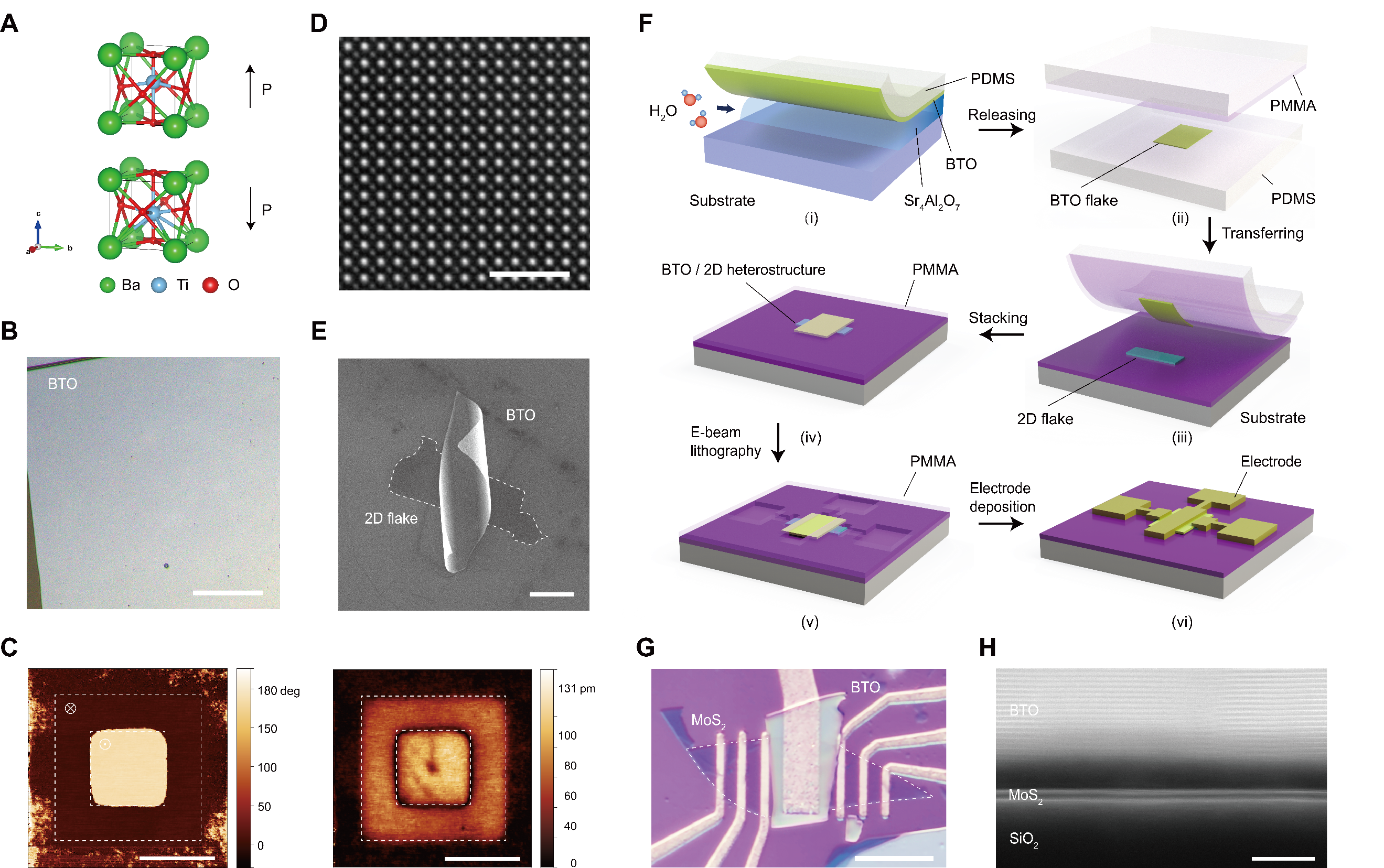

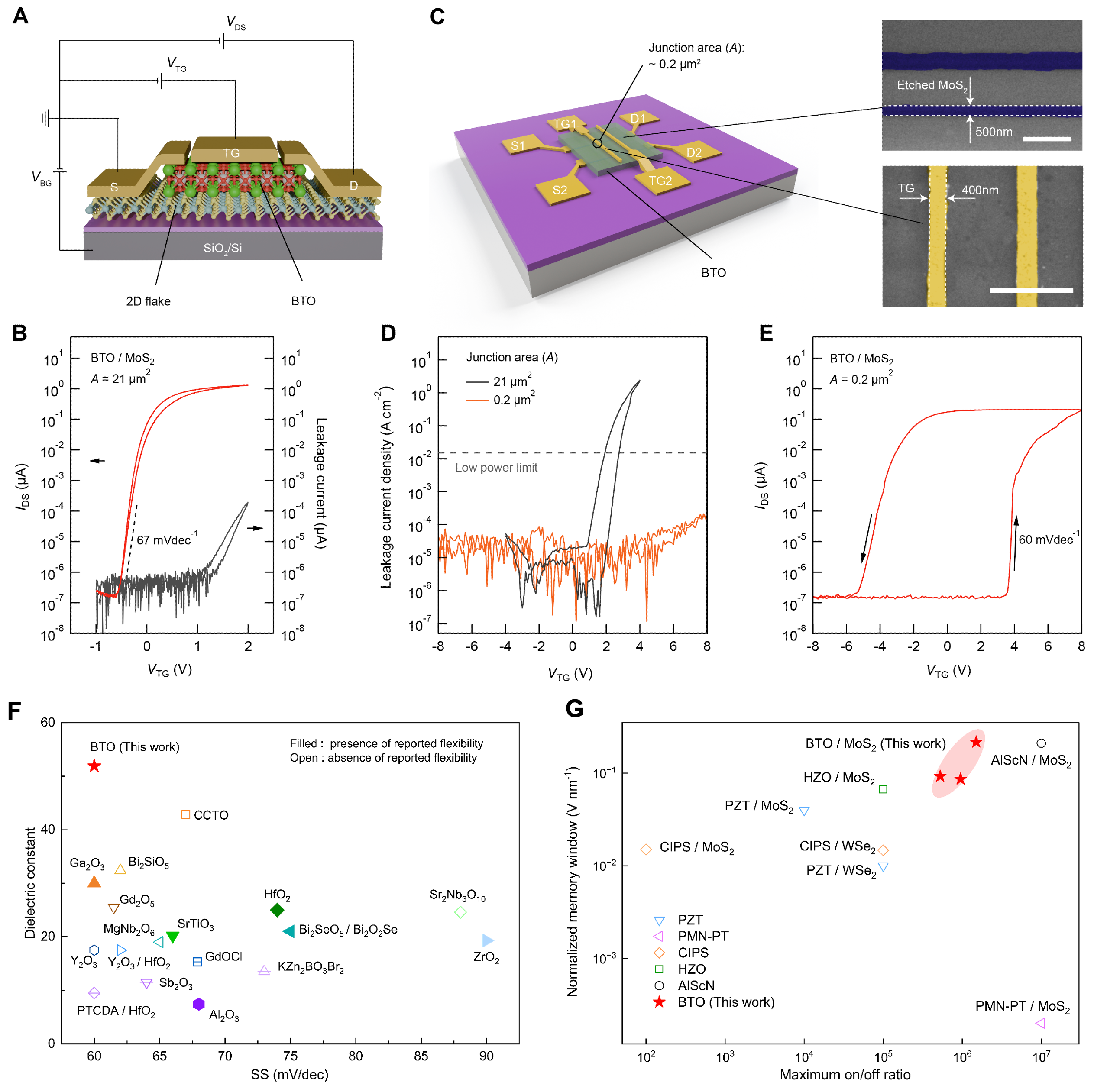

实验中,BTO和Sr4Al3O7(SAOT)薄膜通过脉冲激光沉积在 (001) 取向的 (LaAlO3)0.3 -(SrAl0.5Ta0.5O3)0.7(LSAT)单晶衬底上生长。通过水溶性 SAOT牺牲层技术可以释放得到高质量的自支撑BTO薄膜。利用PMMA辅助转移技术将其转移到二维材料沟道上,并直接蒸镀电极,可以有效限制自支撑薄膜的卷曲,制备出具有均匀范德华间隙的异质结器件。为限制器件漏电流,采用器件微缩化设计。通过电子束光刻和反应离子刻蚀(RIE)将MoS2图案化为500nm宽的条带,BTO 膜通过 PMMA转移到预图案化的MoS2上,然后沉积约400 nm宽的顶栅电极。该策略有效减小了顶栅器件的漏电流,拓宽器件工作电压范围,在无需引入介质阻挡层的情况下实现了本征铁电翻转。

基于上述策略,以BTO作为顶栅介质的FeFET具有优异的高介电常数特性,以及在柔性电子领域的应用潜力。器件具有显著的开关特性,以及良好的的数据保持能力和循环耐久性,展现出应用于非易失存储的潜力。通过与现有器件的性能对标, 证实了BTO/MoS2 FeFET在高性能、低功耗非易失性存储应用中的显著优势。得益于器件稳定的存储窗口,成功构建了3×4晶体管阵列。该阵列借助串联结构,可以实现非易失性的“与”门逻辑操作。此外,阵列中的FeFET可以模拟突触权重更新,在神经网络仿真中展现出良好的识别准确率,验证了该器件用于神经形态计算的可行性。

复旦大学博士生郭泽婧和沙旭洋以及中国科技大学博士生许方是本论文的共同第一作者,沈健教授、郭杭闻研究员和石武青年研究员为论文的共同通讯作者。其他合作者还包括中国科技大学王凌飞教授、复旦大学张成研究员和黄海青年研究员等。该研究获得科技部重点研发计划、国家自然科学基金等项目的资助。

论文链接:https://doi.org/10.1002/advs.202520610

图1 BTO铁电薄膜与二维材料的范德华集成。(A) 钙钛矿 BaTiO3晶体结构与极化状态示意图; (B) 剥离后的大面积自支撑 BTO 薄膜光学图像; (C) PFM验证薄膜的铁电翻转特性; (D) 自支撑 BTO 薄膜的平面 STEM 图像,展示了高质量晶格结构; (E)传统转移中发生卷曲形变的 BTO 薄膜; (F) PMMA 辅助的抗卷曲范德华集成工艺流程示意图; (G) 制备的 BTO/MoS2顶栅晶体管光学图像; (H) 器件沟道区域的截面 STEM 图像,显示均匀的范德华界面。

图2 顶栅BTO/MoS2晶体管的漏电流抑制与器件性能。(A) 以自支撑 BTO 作为顶栅介质的双栅二维晶体管结构示意图; (B) 大结面积器件的转移特性与漏电曲线,显示严重漏电流; (C) 缺陷容忍设计示意图:通过微缩结面积抑制器件漏电; (D) 不同结面积器件的漏电流密度对比,微缩设计显著抑制漏电; (E) 优化后器件的转移特性,展现优异的铁电回滞与开关性能。(F-G) 本工作BTO/MoS2晶体管与现有高 k顶栅 MoS₂ 晶体管(G)和二维铁电晶体管(H)的性能对比。